# Factsheet *SI40UART01*

### Universal Asynchronous Receiver/Transmitter Core

The SI40U550 IP core is a Universal Asynchronous Receiver Transmitter fully compatible with the defacto standard 16550 UART.

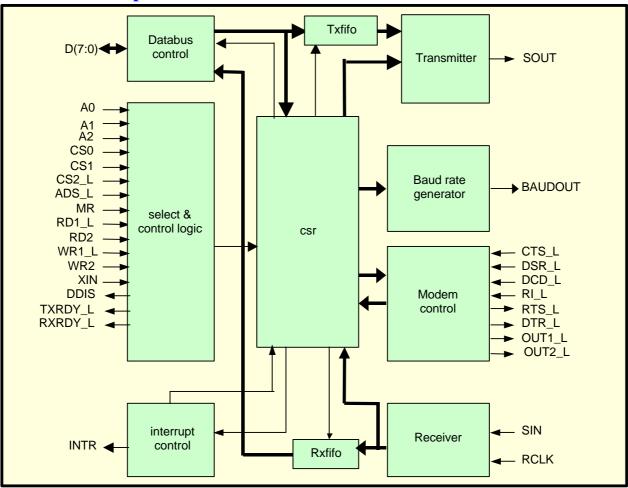

The SI40U550 core performs serial-to-parallel conversions on data received from a peripheral device or modem and parallel-to-serial conversion on data received from the host . The host can read the UART status at any time. The SI40U550 core includes complete modem control capability and a processor interrupt system that can be tailored to minimize software management of the communications link.

The core provides a full-featured transmitterreceiver pair, configurable by software for different speeds, character widths, parity etc. The receiver provides information status with several error indications.

The core can be placed in an alternate FIFO mode. This relieves the CPU of excessive software overhead by buffering received and transmitted characters. The receiver and transmitter FIFOs store up to 16 bytes including three additional bits of error status per byte for the receiver FIFO. In the FIFO mode, there is a selectable auto flow control feature that can significantly reduce software overload and increase system efficiency by automatically controlling serial data flow using RTS output and CTS input signals.

The SI40U550 core includes a programmable baud rate generator capable of dividing a reference clock by divisors from 1 to 65535 and producing a 16x reference clock for the internal transmitter logic. Provisions are included to use this 16xclock for the receiver logic.

DMA operation is allowed with two output signals that inform the DMA controller about when is new received data available and when the UART is able to accept new data for transmission.

Management of modem control outputs and inputs (with their associated interrupt) is included.

## Silicon Cores<sup>™</sup>

Core to the Intelligent Network™

### **Product Features**

- Programmable automated RTS and CTS generation

- In automated CTS mode, CTS controls transmitter

- In automated RTS mode, receive FIFO contents and threshold control RTS

- Fully backward compatible with 16450 UARTs

- In the 16450 mode, Hold and Shift registers eliminate the necessity of precise synchronization between the CPU and serial data

- Programmable aud Rate Generator allows division of any input reference clock by 1 to (216 –1) and generates an internal 16x clock

- Standard asynchronous communication bits (Start, Stop, and Parity) added to or deleted from the serial data stream

- > Independent receiver clock input

- Fully prioritized interrupt system controls

- Transmit, Receive, Line Status, and Data Set interrupts independently controlled

- Fully programmable serial interface characteristics:

- 5-, 6-, 7-, or 8-Bit Characters

- Even-, Odd-, or No-Parity Bit Generation and Detection

- 1-, 1 1/2-, or 2-Stop bit generation

- Baud Generation

- False-start bit detection

- > Extensive status reporting capabilities

- > Line break generation and detection

- Internal diagnostic capabilities:

- Loopback controls for serial link fault isolation

- Break, Parity, Overrun, and Framing error simulation

- Modem control functions (CTS, RTS, DSR, DTR, RI, and DCD)

- > Fully synthesizable RTL Level Verilog core

| UART1.0    | Copyrights © 2002-2003 Silicon Interfaces Private Limited. All rights reserved. |

|------------|---------------------------------------------------------------------------------|

| 12/20/2002 | 606, Nirman Kendra, E. Moses Road, Mahalaxmi, Mumbai 400 011 India              |

|            | www.siliconcores.com and www.siliconinterfaces.com                              |

#### **UART Block Representative Schematic:**

**Contact:**

Email: info@siliconinterfaces.com Phone: (+91-22) 2491 3024;Fax: (+91-22) 2498 1379 In USA: (+1-408) 866 2458; Fax: (+1-408) 866 6586 In UK: (+44-20) 8543 4436; Fax: (+44-20) 8544 1311

**Notice:** Information in this document is indicative. Product specifications are subject to change without notice. *Silicon Interfaces* shall not be responsible for direct, indirect or consequential damages that may accrue through typographical errors or otherwise. No license, expressed or implied to any intellectual property rights is granted by this document. Product names mentioned herein may be trademarks and/or registered trademarks of their respective owners. Rights are hereby acknowledged.

a software and vlsi design center

Silicon Interfaces is the world's answer to integrated solutions for Design Services needs for SOC, ASIC & FPGA for Wireless, Cable & Optical Networking, Fiber Channel & Inter-connect, Data Communications and Storage. Silicon Interfaces is operating since 1990 primarily in USA, Europe and Pacific Rim.

UART1.0 12/20/2002 Copyrights © 2002-2003 *Silicon Interfaces* Private Limited. All rights reserved. 606, Nirman Kendra, E. Moses Road, Mahalaxmi, Mumbai 400 011 India www.siliconcores.com and www.siliconinterfaces.com