802.11N IEEE STANDARD - WIRELESS LAN

Silicon Interfaces® MAC Core for Wireless LAN IEEE 802.11n-2009 incorporates amendment to the IEEE 802.11-2007 wireless networking standard to improve network throughput over the two previous standards - 802.11a and 802.11g - with a significant increase in the maximum raw data rate from 54 Mbit/s to 600 Mbit/s with the use of four spatial streams at a channel width of 40 MHz.

It is designed to handle packetized communication brought about by Spatial Division Multiplexing (SDM). SDM spatially multiplexes multiple independent data streams, transferred simultaneously within one spectral channel of bandwidth. MIMO SDM can significantly increase data throughput as the number of resolved spatial data streams is increased. The basic MAC control time critical functionalities have been implemented in MAC hardware.

This specification describes the functions and services required by an IEEE 802.11 compliant device to operate within ad-hoc and infrastructure networks as well as the station mobility within those networks.

Si24WLAN30 802.11n MAC Core implements the IEEE 802.11n protocol and is backward compatible for a, b and g devices. It is connected to a PCI Host Interface at one end and a BBP PHY with MIMO Interface at the other. The PCI Interface is fully compliant to the PCI Bus Specification 2.0 for a Target device.

It supports transmission and reception of all Frames in the conventional Distributed Coordination Function (DCF) as well as the optional Point Coordination Function (PCF) mode.

• Product Highlights

- Fully backward compliant to IEEE 802.11a, IEEE 802.11b and IEEE 802.11g MAC Layer Functions and Frames.

- A-MPDU Frame Aggregation to the MAC layer for High Throughput (HT) functionality using Block ACK (BA).

- Customizable to work with most PHY devices for 802.11n with MIMO and 40 MHz channels.

- Supports the role of Station (STA) as well as that of Access Point (AP).

- Supports both Active as well as Passive Scanning mode of operation.

- STA operates in both Infrastructure BSS as well as Independent BSS (IBSS) mode.

- Supported Data Rates up to 150 Mbit/s (802.11n), 54 Mbit/sec (802.11a and 802.11g) and 11 Mbit/sec (802.11b).

- Performs CSMA/CA (Random Backoff) Algorithm to access the medium.

- PCI Bus Interface (Target).

- 4K Internal RAM for Transmission and Reception of Frames.

- Synchronizers implemented to handle operations between the PCI Clock domain and the relatively slower PHY Clock domain.

• Product Specifications

- Fully Synthesizable Register Transfer Level (RTL) VHDL.

- Test Bench Environment: VHDL.

- Targeted to Xilinx Spartan-6

- Max. Clock Frequency - 75 MHz

• Product Options

Adaptations: Any PHY specific BBP Interface with Multiple-input Multiple-output (MIMO) 40 MHz Channels

Add-ons : PCI Memory Cycle Operations

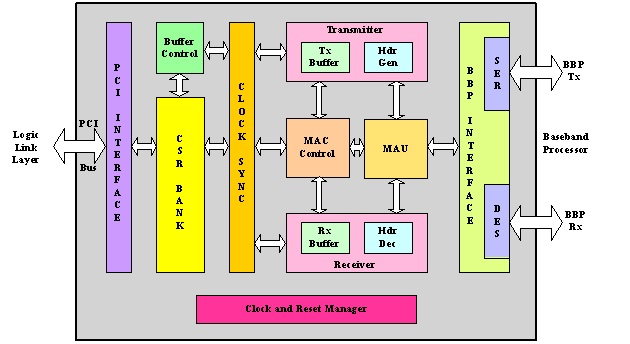

Si24WLAN30 MAC Core Block Representative Schematic:

MAC Controller: Centrally controls the MAC Sub-Module operations. Takes the decision of which packet to be transmitted next. Interacts with MAU, Transmitter, Receiver and HAU for the MAC operations to be performed. It is designed to handle aggregation of frames through Block Acknowledgement.

• Brief description of MAC Modules

HAU: Header Assembly Unit prepares the Header of the packet as indicated by the MAC Controller.

MAU: Implements CSMA/CA (Random Backoff) Algorithm to access the medium.

Transmitter: Transmits the frame by sequentially arranging the packet fields and appending it with CRC bytes

Receiver: Receives and checks the incoming frame for Destination Address, CRC, packet length etc.

BBP Interface: Interacts with the PHY Layer to transfer frames in and out of the MAC.

PCI Interface:Provides the necessary interface between the MAC and LLC. It implements the complete functionality of a Target device in compliance with the PCI Bus Specification 2.0.

Buffer Control: Generates the appropriate Green Flags (signals) for transmission and reception of frames.

Clock Synchronizer: Provides the necessary synchronization between the PCI Clock domain signals and the relatively slower PHY clock domain signals.

CSR Bank:Holds the Bank of Configuration and Status Registers.

Clock and Reset Manager: Provides the required clock through a DCM and an Active-high pulse to reset all the MAC Sub-modules.

• Applications :

- Voice Over IP (VOIP)

- Wireless LAN STA terminal (could be a Mobile Phone, PDA, Tablet, Laptop or PC)

- Wireless Home/Office Access Point Networking Devices

- Wireless Audio, Video, Consumer electronics

- Gaming

- Wireless LAN Adapter

Notice: Information in this document is indicative. Product specifications are subject to change without notice. Silicon Interfaces shall not be responsible for direct, indirect or consequential damages that may accrue through typographical errors or otherwise. No license, expressed or implied to any intellectual property rights is granted by this document. Product names mentioned herein may be trademarks and/or registered trademarks of their respective owners. Rights are hereby acknowledged.

Copyright © 2002-2014 Silicon Interfaces Private Limited. All rights reserved.

For more information please contact Silicon Cores at info@siliconinterfaces.com

<Previous product | Next product>

802.11N IEEE STANDARD - WIRELESS LAN

Silicon Interfaces® MAC Core for Wireless LAN IEEE 802.11n-2009 incorporates amendment to the IEEE 802.11-2007 wireless networking standard to improve network throughput over the two previous standards - 802.11a and 802.11g - with a significant increase in the maximum raw data rate from 54 Mbit/s to 600 Mbit/s with the use of four spatial streams at a channel width of 40 MHz.

It is designed to handle packetized communication brought about by Spatial Division Multiplexing (SDM). SDM spatially multiplexes multiple independent data streams, transferred simultaneously within one spectral channel of bandwidth. MIMO SDM can significantly increase data throughput as the number of resolved spatial data streams is increased. The basic MAC control time critical functionalities have been implemented in MAC hardware.

This specification describes the functions and services required by an IEEE 802.11 compliant device to operate within ad-hoc and infrastructure networks as well as the station mobility within those networks.

Si24WLAN30 802.11n MAC Core implements the IEEE 802.11n protocol and is backward compatible for a, b and g devices. It is connected to a PCI Host Interface at one end and a BBP PHY with MIMO Interface at the other. The PCI Interface is fully compliant to the PCI Bus Specification 2.0 for a Target device.

It supports transmission and reception of all Frames in the conventional Distributed Coordination Function (DCF) as well as the optional Point Coordination Function (PCF) mode.

• Product Highlights

- Fully backward compliant to IEEE 802.11a, IEEE 802.11b and IEEE 802.11g MAC Layer Functions and Frames.

- A-MPDU Frame Aggregation to the MAC layer for High Throughput (HT) functionality using Block ACK (BA).

- Customizable to work with most PHY devices for 802.11n with MIMO and 40 MHz channels.

- Supports the role of Station (STA) as well as that of Access Point (AP).

- Supports both Active as well as Passive Scanning mode of operation.

- STA operates in both Infrastructure BSS as well as Independent BSS (IBSS) mode.

- Supported Data Rates up to 150 Mbit/s (802.11n), 54 Mbit/sec (802.11a and 802.11g) and 11 Mbit/sec (802.11b).

- Performs CSMA/CA (Random Backoff) Algorithm to access the medium.

- PCI Bus Interface (Target). (Target).

- 4K Internal RAM for Transmission and Reception of Frames.

- Synchronizers implemented to handle operations between the PCI Clock domain and the relatively slower PHY Clock domain.

• Product Specifications

- Fully Synthesizable Register Transfer Level (RTL) VHDL.

- Test Bench Environment: VHDL.

- Targeted to Xilinx Spartan-6

- Max. Clock Frequency - 75 MHz

• Product Options

Adaptations: -Any PHY specific BBP Interface with Multiple-input Multiple-output (MIMO) 40 MHz Channels

Add-ons : -PCI Memory Cycle Operations

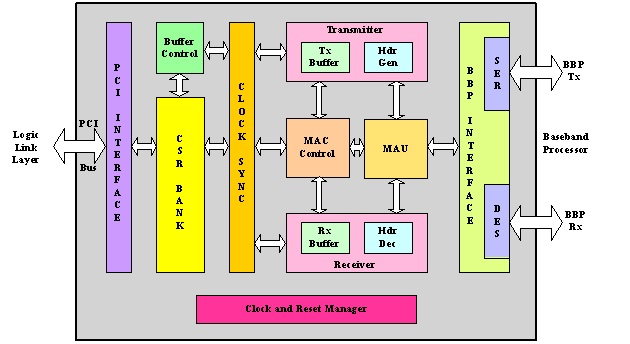

Si24WLAN30 MAC Core Block Representative Schematic:

MAC Controller: Centrally controls the MAC Sub-Module operations. Takes the decision of which packet to be transmitted next. Interacts with MAU, Transmitter, Receiver and HAU for the MAC operations to be performed. It is designed to handle aggregation of frames through Block Acknowledgement.

• Brief description of MAC Modules

HAU: Header Assembly Unit prepares the Header of the packet as indicated by the MAC Controller.

MAU: Implements CSMA/CA (Random Backoff) Algorithm to access the medium.

Transmitter: Transmits the frame by sequentially arranging the packet fields and appending it with CRC bytes

Receiver: Receives and checks the incoming frame for Destination Address, CRC, packet length etc.

BBP Interface: Interacts with the PHY Layer to transfer frames in and out of the MAC.

PCI Interface:Provides the necessary interface between the MAC and LLC. It implements the complete functionality of a Target device in compliance with the PCI Bus Specification 2.0.

Buffer Control: Generates the appropriate Green Flags (signals) for transmission and reception of frames.

Synchronizer: Provides the necessary synchronization between the PCI Clock domain signals and the relatively slower PHY clock domain signals.

CSR Bank:Holds the Bank of Configuration and Status Registers.

Clock and Reset Manager: Provides the required clock through a DCM and an Active-high pulse to reset all the MAC Sub-modules.

• Applications :

- Voice Over IP (VOIP)

- Wireless LAN STA terminal (could be a Mobile Phone, PDA, Tablet, Laptop or PC)

- Wireless Home/Office Access Point Networking Devices

- Wireless Audio, Video, Consumer electronics

- Gaming

- Wireless LAN Adapter

Notice: Information in this document is indicative. Product specifications are subject to change without notice. Silicon Interfaces shall not be responsible for direct, indirect or consequential damages that may accrue through typographical errors or otherwise. No license, expressed or implied to any intellectual property rights is granted by this document. Product names mentioned herein may be trademarks and/or registered trademarks of their respective owners. Rights are hereby acknowledged.

Copyright © 2002-2014 Silicon Interfaces Private Limited. All rights reserved.

For more information please contact Silicon Cores at info@siliconinterfaces.com

<Previous product | Next product>